INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING ol. 4. Issue 5. May 2016

# Design and Analysis of Hybrid 1-Bit Full Adder Circuit and Its Impact on 2-Bit Comparator: **A** Review

## Rachana S<sup>1</sup>, Roshan Shetty<sup>2</sup>, Praveen J<sup>3</sup>, Raghavendra Rao A<sup>4</sup>

M.Tech Student, Dept. of ECE, Alva's Institute of Engineering & Technology, Mijar, Moodbidri, Karnataka, India<sup>1</sup> Assistant Professor, Dept. of ECE, Alva's Institute of Engineering & Technology, Mijar, Moodbidri, Karnataka, India<sup>2</sup>

Sr. Associate Professor, Department of ECE, Alva's Institute of Engineering & Technology, Mijar, Moodbidri,

### Karnataka, India<sup>3,4</sup>

Abstract: In this paper, a hybrid 1-bit full adder design employing both complementary metal-oxide-semiconductor (CMOS) logic and transmission gate logic is reported and it is incorporated in a 2-bit comparator design. The circuit was implemented using Tanner tools. Performance parameters such as power, delay, and layout area were compared with the existing designs such as classical CMOS full adder(C-CMOS), complementary pass-transistor logic(CPL), transmission gate adder(TGA) and so on. In comparison with the existing full adder designs, the present implementation was found to offer significant improvement in terms of power and speed and thus in a 2-bit comparator design.

Keywords: Carry propagation adder, hybrid design, low power, CMOS (Complementary Metal Oxide Semiconductor), high speed, Tanner tool.

### I. **INTRODUCTION**

like cellular phones, personal digital assistants (PDAs) and known notebooks demand VLSI and ultra large-scale integration implementation. These designs exploit the features of designs with an improved power delay characteristics. Full adders, being one of the most fundamental building blocks of all the aforementioned circuit applications, remain a key focus domain of the researchers over the years. Different logic styles, each having its own merits and bottlenecks, was investigated to implement 1-bit full adder cells. Adder core is the most critical building block in microprocessors and digital signal processors. In general, a one-bit full adder core has three inputs (A, B, and carry in Ci) and two outputs (sum S and carry out Co). The complex arithmetic circuits such as subtraction, multiplication, and division functions usually can be realized by co-operations of multiple adders. An adder performance affects the arithmetic system as a whole.

The designs, reported so far, may be broadly classified into two categories:

- 1) static style and

- 2) dynamic style.

Static full adders are generally more reliable, simpler with less power requirement but the on chip area requirement is usually larger compared with its dynamic counterpart.

Different logic styles tend to favor one performance aspect at the expense of others. Standard static CMOS, dynamic CMOS logic, complementary pass-transistor logic (CPL), and transmission gate full adder (TGA) are the most styles in order to improve the overall performance. important logic design styles in the conventional domain.

Increased usage of the battery-operated portable devices The other adder designs use more than one logic style, as hybrid-logic design style, for their different logic styles to improve the overall performance of the full adder.

> The advantages of standard complementary (CMOS) style-based adders (with 28 transistors) are its robustness against voltage scaling and transistor sizing; while the disadvantages are high input capacitance and requirement of buffers. Another complementary type smart design is the mirror adder with almost same power consumption and transistor count (as that of) but the maximum carry propagation path/delay inside the adder is relatively smaller than that of the standard CMOS full adder. On the other hand, CPL shows good voltage swing restoration employing 32 transistors. However, CPL is not an appropriate choice for low-power applications. Because of its high switching activity of intermediate nodes (increased switching power), high transistor count, static inverters, and overloading of its inputs is the bottleneck of this approach.

> The prime disadvantage of CPL, that is, the voltage degradation was successfully addressed in TGA, which uses only 20 transistors for full adder implementation. However, the other drawbacks of CPL like slow-speed and high-power consumption remain an area of concern for the researchers. Later, researchers focused on the hybrid logic approach which exploited the features of different logic Although the hybrid logic styles offers promising

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 4. Issue 5. May 2016

performance, most of these hybrid logic adders suffered weak inverter (channel width of transistors being small) from poor driving capability issue and their performance formed by transistors Mp1 and Mn1 [Fig. 1(b)]. Full swing degrades drastically in the cascaded mode of operation if of the levels of output signals is guaranteed by level the suitably designed buffers are not included.

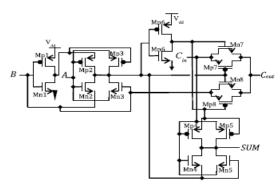

The main objective of this paper is to improve the transistor arrangement. The modified XNOR presented in different performance parameters like power, delay, and transistor count of the full adder compared with the already existing ones and incorporating them into a 2-bit **B. Carry Generation Module** comparator. The circuit was implemented using Tanner tools. The average power consumption of the proposed circuit reduced dramatically by was deliberate incorporation of very weak CMOS Inverters coupled with strong transmission gates.

### **II. FULL ADDER ARCHITECTURE**

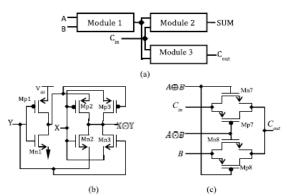

The proposed full adder circuit is represented by three blocks as shown in Fig. 1(a). Module 1 and module 2 are the XNOR modules that generate the sum signal (SUM) and module 3 generates the output carry signal (Cout). Each module is designed individually such that the entire Literature survey is an important part of the project. It adder circuit is optimized in terms of power, delay, and area. These modules are discussed below in detail.

Fig. 1. (a) Schematic structure of proposed full adder. (b) XNOR module. (c) Carry generation module.

Fig 2. Detail circuit diagram of proposed full adder

### A. Modified XNOR Module

In the proposed full adder circuit, XNOR module is responsible for most of the power consumption of the entire adder circuit. Therefore, this module is designed to minimize the power to the best possible extend with avoiding the voltage degradation possibility. Fig. 1(b) consumption is reduced significantly by deliberate use of newly full adder has been designed using hybrid-CMOS

restoring transistors Mp3 and Mn3 [Fig. 1(b)]. In this paper, the XNOR module employed 6 T, having different this paper offers low-power and high-speed.

In the proposed circuit, the output carry signal is implemented by the transistors Mp7, Mp8, Mn7, and Mn8 as shown in Fig. 1(c). The input carry signal (Cin) propagates only through a single transmission gate (Mn7 and Mp7), reducing the overall carry propagation path significantly. The deliberate use of strong transmission gates (channel width of transistors Mn7, Mp7, Mn8, and Mp8 is made large) guaranteed further reduction in propagation delay of the carry signal.

### **III. LITERATURE SURVEY**

enables assimilation of knowledge required for the project right from the problem definition, finding a solution for the same and its execution. The following section summarizes the literature survey carried out for the project.

Kiran R. Barapatre, Mayur B. Petkar, Asmita R. Padole explains the concept of "CMOS Full Adder for Energy Efficient Arithmetic Applications"[1]. In this, they say that Energy-Efficiency is one of the most required features in digital electronic systems for high-performance and/or portable applications which signify PDP, it measures the energy consumed per switching event. Also, they proved complementary CMOS is the logic style of choice for the implementation of combinational circuits, if low voltage, low power, and small power-delay products are of concern with relatively low area.

Mohammad Javad Zavarei, Ehsan Kargaran designed 1-bit full adder using hybrid-CMOS logic style presented a paper entitled as "Design of new full adder cell using hybrid-CMOS logic style"[2]. The new full adder is based on a novel XOR-XNOR circuit that outperforms its best counterpart showing 28% improvement in powerdelay product (PDP). Design of proposed full adder is based on improvement in the PDP and it provides fullswing output with good driving capability. Simulations demonstrate that full adder successfully operates in the PDP compared to similar circuits.

"Design Analysis of XOR (4T) based Low Voltage CMOS Full Adder Circuit"[3], is a paper presented by Subodh Wairya, Garima Singh, Vishant, R. K. Nagaria, S. Tiwari. In this performance analysis of 1-bit full adder cell has been presented. Different adder logic styles have been implemented, simulated, analyzed and compared. Using the adder categorization and hybrid-CMOS design shows the modified XNOR circuit where the power style, many full adders can be conceived. As an example,

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL. ELECTRONICS. INSTRUMENTATION AND CONTROL ENGINEERING /ol. 4. Issue 5. Mav 2016

design style with pass transistor are presented that targets speed properties, both the new exclusive OR circuit and low PDP. The XOR based hybrid-CMOS full adder shows the new full adder can be efficiently integrated in a better performance than most of the other standard full- system-on-a-chip (SoC) or an embedded system[8]. adder cells owing to the new design modules analysis is discussed.

"Architecture Of Adders Based On Speed, area And **Power dissipation**"[4], is a paper presented by Prashanth.P and Prabhu Swamy. In this a stacking pMOS transistor is introduced in 10-T and 11-T adder cells to reduce the leakage current of the circuit. Due to reduction of leakage current the power consumption is reduced. These adder circuits can be used for low power applications.

The paper entitled as "Hybrid adders for high-speed arithmetic circuits: a comparison"[5], presented by Monico Linares Aranda, Ramon Báez, Oscar Gonzalez Diaz. In this paper the most interesting topologies of onebit hybrid full adders, are analyzed and compared for speed, power consumption, and power-delay product. Performance has been also compared for different supply voltage values. The simulation results show that the Chang adder is the best in terms of PDP figure of merit, however the Aguirre adder is the best in terms of driving capability even at low power supply.

The paper entitled "A novel low-power full-adder cell for low voltage"[6], presented by Keivan Navi Mehrdad Maeen, Vahid Foroutan, Somayeh Timarchi, Omid Kavehei. They presents a novel low-power majority function-based 1-bit full adder that uses MOS capacitors (MOSCAP) in its structure. It can work reliably at low supply voltage. In this design, the time-consuming XOR gates are eliminated. The circuits being studied are optimized for energy efficiency at 0.18-µm CMOS process technology. The adder cell is compared with seven widely used adders based on power consumption, speed, powerdelay product (PDP) and area efficiency.

Keivan Navi, Mohammad Hossein Moaiyeri, Reza Faghih Mirzaee, Omid Hashemipour, Babak Mazloom Nezhad proposed a concept of "Two new low-power Full Adders based on majority-not gates"[7]. Two novel low-power 1-bit Full Adder cells have been proposed. Both circuits use only two majority-not gates, which are implemented using new methods. The first design used only capacitors and CMOS inverter gates, while the second one has benefited from a high-performance CMOS bridge circuit, which has improved the parameters of the first design. Low power consumption has been targeted at the circuit design level for both cells.

Chiou-Kou Tung, Yu-Cherng Hung gives the idea about new three-input exclusive OR (3-XOR) design, the new hybrid full adder is composed of pass-transistor logic and static CMOS logic. The main design objectives for the full adder core are providing not only low power and high speed but also with driving capability. The circuit is A. M. Shams, T. K. Darwish, M. A. Bayoumi presented proven to have the minimum power consumption and the a paper entitled "Performance analysis of low-power 1fastest response of carry out signal among the adders bit CMOS full adder cells"[13]. Here adder cell is selected for comparison. Due to the low-power and high- anatomized into smaller modules. The modules are studied

Sumeer Goel, Ashok Kumar and Magdy A. Bayoumi presented a paper entitled "Robust, Energy-Efficient Full Adders for Deep-Submicrometer Design Using Hybrid-CMOS Logic Style"[9]. The proposed hybrid-CMOS full adder has better performance than most of the standard full-adder cells. It performs well with supply voltage scaling and under different load conditions. When embedded in a four-operand CSA, it outperforms all the other adders making it suitable for larger adders. The proposed adder has better noise immunity as compared to the standard adder such as static CMOS, making it suitable for deep-submicrometer operation. We recommend the use of hybrid-CMOS design style for the design of highperformance circuits.

"A Review of 0.18-um Full Adder Performances for Tree Structured Arithmetic Circuits"[10], is a paper presented by Chip-Hong Chang, Jiangmin Gu and Mingyan Zhang, says that for full adder cell design, passlogic circuit is thought to be dissipating minimal power and have smaller area because it uses less number of transistors. A hybrid full adder cell consisting of the XOR/XNOR, sum and carry out sub circuits, is proposed. The pass logic design style is used to efficiently generate the XOR and XNOR functions simultaneously and a good drivability carry out is generated by a complementary CMOS style circuit with regular layout.

Mingvan Zhang, Jiangmin Gu and Chip-Hong Chang presented a paper titled as "A novel hybrid pass logic with static CMOS output drive full-adder cell",[11]. In this, investigation resulted in A novel design of a 1-bit full adder cell featuring hybrid CMOS logic style where the pass logic style has been used to efficiently generate the XOR and XNOR functions simultaneously and a good drivability carry out has been generated by a novel complementary CMOS style with regular structure. The circuit has shown to be power-delay efficient over a wide supply voltage ranges above 2.4V and is therefore suitable for constructing low power, high performance arithmetic logic unit for embedded applications

"Novel Design Methodology for High-Performance XOR-XNOR Circuit Design"[12], is a paper proposed by Sumeer Goel, Mohamed A. Elgamel and Magdy A. Bayoumi. Here they proposed and tested a novel design methodology for noise-immune low voltage XOR-XNOR circuits. The performance of the proposed circuits has been shown to outperform the compared ones, which can operate at low-voltages, and have good output levels. The proposed circuits haves been tested to be much noiseimmune, energy-efficient and faster than the compared ones

INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL. ELECTRONICS. INSTRUMENTATION AND CONTROL ENGINEERING Vol. 4, Issue 5, May 2016

and evaluated extensively. Several designs of each of them [2]. M. J. Zavarei, M. R. Baghbanmanesh, E. Kargaran, H. Nabovati, are developed, prototyped, simulated and analyzed. Twenty different 1-bit full-adder cells are constructed (most of them are novel circuits) by connecting [3]. combinations of different designs of these modules. Each of these cells exhibits different power consumption, speed, area, and driving capability figures. Two realistic circuit structures that include adder cells are used for simulation.

### **IV. APPLICATIONS**

1) Hassoune, D.Flandre, I.O'Connor & J. Legat proposed a new structure of a hybrid full adder, namely, the branch based logic and pass-transistor (BBL-PT) cell, which is implemented by combining branch-based logic and pass-transistor logic. This leads to tremendous benefit for multiplier application. Also, the implementation of an 8-bit ripple carry adder based on the ULPFA is described. and comparisons between adders based on full adders [8]. from the prior art and ULPFA version demonstrate that development outperforms the static CMOS and the CPL full adders, particularly in terms of power consumption [9]. and PDP by at least a factor of two[14].

2) **D.Radhakrishnan** designed new adder cell that does not suffer from the threshold voltage drop in MOS transistors, but at the same time uses fewer transistors. This new cell can easily be adopted for low voltage operation as long as the supply voltage is not allowed to fall below 2|Vip|. This cell can then function as a library cell for the future design of low-power CMOS [12]. S. Goel, M. Elgamel, and M. A. Bayoumi, "Novel design combinational circuits[15].

3) M. Alioto, G. Di Cataldo, G. Palumbo presented a paper which deals with the implementation of Full Adder chains by mixing different CMOS Full Adder topologies. The approach is based on cascading fast Transmission-Gate Full Adders interrupted by static gates having driving capability, such as inverters, thus exploiting the intrinsic low power consumption of such topologies. The obtained mixed-topology circuits are optimized in terms of delay by resorting to simple analytical models[16].

### V.CONCLUSION

In this paper, a low-power hybrid 1-bit full adder has been proposed. The simulation was carried out using Tanner tool in 45-nm technology and compared with other standard design approaches like CMOS, CPL, TFA, TGA. The simulation results established that the proposed adder offered improved PDP compared with the earlier reports. The efficient coupling of strong transmission gates driven by weak CMOS inverters lead to fast switching speeds, lesser layout area. The proposed full adder is used in comparator design and results are compared with standard design approaches.

### REFERENCES

[1]. Kiran R. Barapatre, Mayur B. Petkar, Asmita R. Padole "CMOS full-adders for energy-efficient arithmetic applications," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 4, pp. 718-721. Apr. 2011.

- and A. Golmakani, "Design of new full adder cell using hybrid-CMOS logic style," in Proc. 18th IEEE Int. Conf. Electron., Circuits Syst. (ICECS), Dec. 2011, pp. 451-454.

- S. Wairya, G. Singh, R. K. Nagaria, and S. Tiwari, "Design analysis of XOR (4T) based low voltage CMOS full adder circuit," in Proc. IEEE Nirma Univ. Int. Conf. Eng. (NUiCONE), Dec. 2011, pp. 1-

- [4]. P. Prashanth and P. Swamy, "Architecture of adders based on speed, area and power dissipation," in Proc. World Congr. Inf. Commun. Technol. (WICT), Dec. 2011, pp. 240-244.

- [5]. M. L. Aranda, R. Báez, and O. G. Diaz, "Hybrid adders for highspeed arithmetic circuits: A comparison," in Proc. 7th IEEE Int. Conf. Elect. Eng. Comput. Sci. Autom. Control (CCE), Tuxtla Gutierrez, NM, USA, Sep. 2010, pp. 546-549.

- K. Navi, M. Maeen, V. Foroutan, S. Timarchi, and O. Kavehei, "A novel low-power full-adder cell for low voltage," VLSI J. Integr., vol. 42, no. 4, pp. 457-467, Sep. 2009.

- H. T. Bui, Y. Wang, and Y. Jiang, "Design and analysis of low-[7]. power 10-transistor full adders using novel XOR-XNOR gates," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 49, no. 1, pp. 25-30, Jan. 2002.

- C.-K. Tung, Y.-C. Hung, S.-H. Shieh, and G.-S. Huang, "A lowpower high-speed hybrid CMOS full adder for embedded system," in Proc.IEEE Conf. Design Diagnostics Electron. Circuits Syst., vol. 13.Apr. 2007, pp. 1-4.

- S. Goel, A. Kumar, and M. A. Bayoumi, "Design of robust, energy efficient full adders for deep-submicrometer design using hybrid-CMOS logic style," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 14, no. 12, pp. 1309-1321, Dec. 2006.

- [10]. C. H. Chang, J. M. Gu, and M. Zhang, "A review of  $0.18\text{-}\mu\text{m}$  full adder performances for tree structured arithmetic circuits," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 13, no. 6, pp. 686-695, Jun. 2005.

- [11]. M. Zhang, J. Gu, and C.-H. Chang, "A novel hybrid pass logic with static CMOS output drive full-adder cell," in Proc. Int. Symp. Circuits Syst., May 2003, pp. 317-320.

- methodology for high-performance XOR-XNOR circuit design," in Proc. 16th Symp. Integr. Circuits Syst. Design (SBCCI), Sep. 2003, pp. 71-76.

- [13]. A. M. Shams, T. K. Darwish, and M. A. Bayoumi, "Performance analysis of low-power 1-bit CMOS full adder cells," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 10, no. 1, pp. 20-29, Feb. 2002.

- [14]. D. Radhakrishnan, "Low-voltage low-power CMOS full adder," IEE Proc.-Circuits Devices Syst., vol. 148, no. 1, pp. 19-24, Feb. 2001.

- [15]. I. Hassoune, D. Flandre, I. O'Connor, and J. Legat, "ULPFA: A new efficient design of a power-aware full adder," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 8, pp. 2066-2074, Aug. 2010.

- [16]. M. Alioto, G. Di Cataldo, and G. Palumbo, "Mixed full adder topologies for high-performance low-power arithmetic circuits," Microelectron. J., vol. 38, no. 1, pp. 130-139, Jan. 2007.